# A-SSCC 2025 Review

한국과학기술원 전기및전자공학부 박사과정 윤웅노

## Session 6 High-Performance Frequency Generation

이번 2025 A-SSCC의 Session 6, High-Performance Frequency Generation은 총 4 편의 논문이 발표되었다. 6.1과 6.2에서는 spur와 noise를 줄이기 위한 보상 기법을 도입하였으며, 6.4는 sampling PLL에서 DSM으로 인한 quantization noise cancellation을 위한 방안을 제안하였다. 또한, 6.1과 6.4에서는 각각 PD-less, DTC-less 구조를 제안하여 기존에 사용하던 아날로그 블록들을 제거하고 그 역할을 내재화하려는 방향성을 보여주었다.

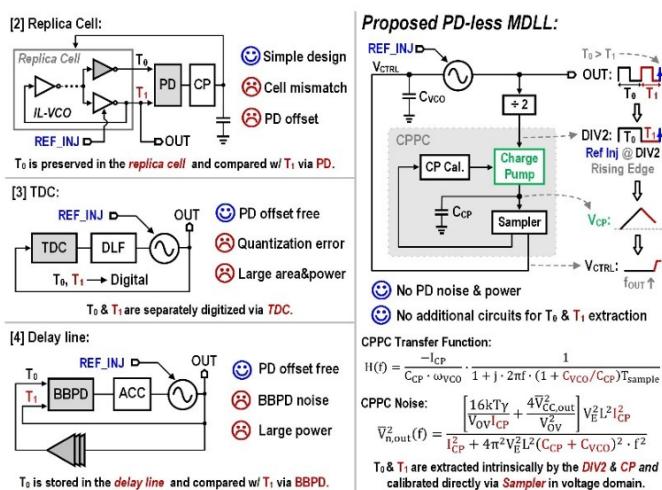

**#6-1** Multiplying delay-locked loop(MDLL)은 injection locked loop의 한 종류로, ring oscillator(RO)의 phase noise suppression과 동시에 넓은 BW를 챙길 수 있는 장점을 가진다. 그러나 reference frequency를 직접 injection 시켜주는 경우 reference spur가 크게 유발되는 이슈가 있다. 이를 해결하기 위해 최근 연구들은 frequency tracking loop (FTL)을 도입하여 RO free-running 주기 ( $T_0$ )를 reference 주기와 일치시키려는 시도를 해왔다. 대표적인 예시로는, 1) 직접 RO에 injection 하는 것이 아닌, replica cell에 injection을 시킨 후 PD/CP를 통해 차이를 보정하는 방식, 2) TDC를 이용하여 reference와  $T_0$  각각을 디지털 값으로 변환하여 보정하는 방식, 3)  $T_0$ 와 동일한 크기의 delay를 가진 delay line을 도입하여  $T_0$ 를 저장하고 reference와 비교하는 방식 등이 존재하였다. 하지만 이들은 각각 cell mismatch에 취약함, TDC의 resolution-power trade-off, BBPD의 noise 기여와 delay line의 resolution-power trade-off라는 한계를 지니고 있다.

[그림 1] 기존 MDLL에서의 FTL들 (좌), 제안된 PD-less MDLL (우)

본 논문은 PD-less RO-based MDLL 구조에 charge-pump phase corrector (CPPC)를 통한 FTL을 구현하여 reference spur를 억제하면서도 noise source를 최소화하는 FTL을 제안하였다. 65nm 공정에서  $0.014\text{mm}^2$ 의 작은 면적으로 구현되었으며, 78.8fs의 우수한 RMS jitter 성능을 달성하였다. 핵심이 되는 CPPC는 reference가 injection되는 경우 CP의 up-down pulse width가 바뀌는 특성을 이용하여 시간 차이를 전압으로 바꾸는 역할을 한다. 그렇게 바뀐 전압 값을 기준으로 RO의 주파수를 변경하여, 결과적으로는 reference 주파수와 동일하게 동작하도록 한다. 회로 구현 측면에서는 charge sharing에 의한 에러를 방지하기 위해 calibration phase를 도입하여 전압을 유지하는 기법과, 홀수 N 배수 동작 시 위상 불일치로 인한 오동작을 막기 위한 mode selection 기법을 적용하여 완성도를 높였다.

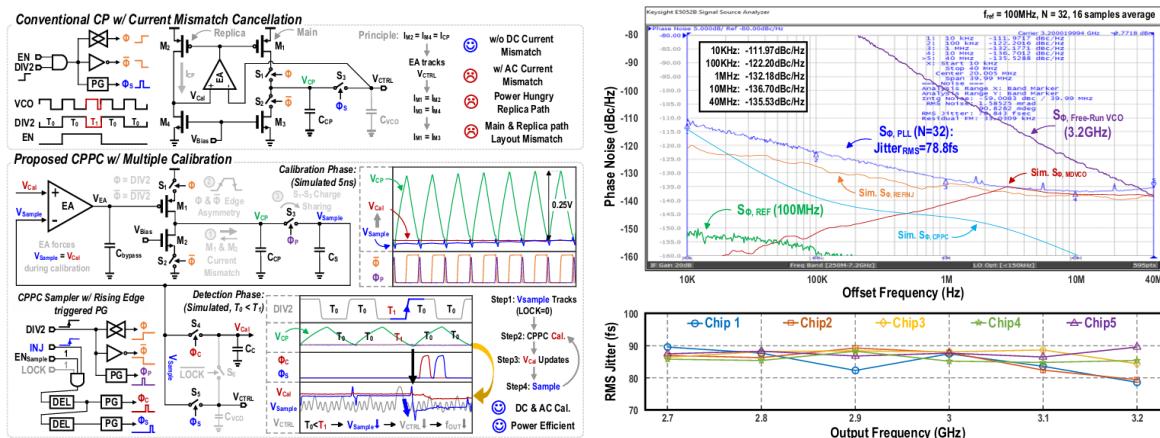

[그림 2] 기존 CP 전류 mismatch cancellation 구조와 제안된 CPPC에서 기울기/전류 mismatch의 해결 (좌) 측정/시뮬레이션 phase noise 결과와 5개 칩에 대해 측정된 RMS jitter (우)

성능적으로는  $-250.2 \text{ FoM}_R$ 을 달성하여 power 소모 대비 매우 우수한 RMS jitter 값을 지닌다. 특히, power breakdown을 보아도 79%에 해당하는 전력을 RO가 소모하고 있기에 noise-power 최적화가 잘 이루어진 설계로 판단된다. 다만, 홀수 N 모드에서는 Loop BW가 절반으로 바뀌는 특성이 있으며, comparison table에 제시된 RMS jitter 값은 측정된 5개의 샘플 중 가장 좋은 성능을 보인 칩의 결과라는 점은 성능 해석에 감안해야 할 부분이다.

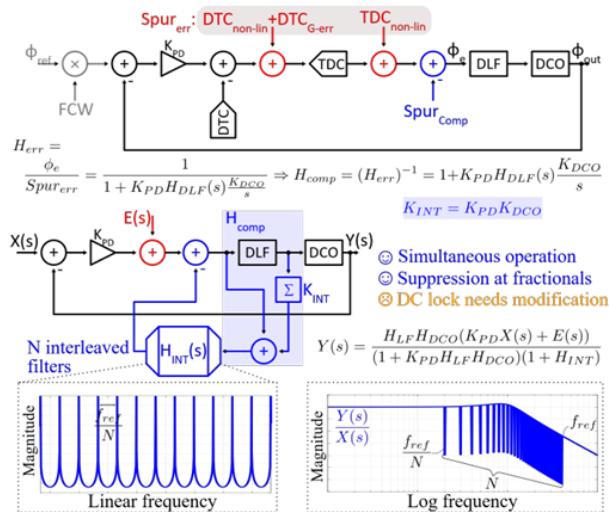

**#6-2 Fractional-N Digital PLL (DPPLL)**은 scalability와 작은 면적 측면에서 유리하여 무선 transceiver를 위해 많이 사용되지만, 신호 왜곡과 간섭을 유발하며 phase noise 성능을 저하시키는 fractional spur가 고질적인 이슈로 지적되어 왔다. Fractional spur는 주로 PD의 non-ideality로 인하여 발생하며, 기존의 digital pre-distortion (DPD)를 통해 해결하는

접근은 DTC의 정확도, dithering을 쓰는 방법은 높아진 noise floor가 issue로 존재하였다. 본 논문은 이러한 한계를 all-digital spur compensation (ADSC) 기법을 통하여 해결하고자 하였다. 이 기법은 여러 신호가 loop-dynamics에 포함되어 직접 조정하기 어렵다는 점에서 착안하여, 디지털 신호에 inverse transfer function을 적용해 보상 신호를 생성한다.

[그림 3] TDC 기반 DPLL 모델링과 제안된 ADSC의 원리 모식도

구체적으로는, N개의 interleaved integrators를 사용하여 PLL의 transfer function에서 fractional tone이 나타나는 지점마다 zero를 만들어 각각의 spur를 필터링하는 방식이다. 이러한 방식으로 이전의 아날로그 DTC calibration과는 다르게 그 어떤 왜곡 신호이든 주기적이면 모두 보상할 수 있기에, 복잡한 LMS 알고리즘 없이도 DTC gain error, 신호의 기울기 왜곡, ADC에서의 cap. Mismatch 등을 모두 보상할 수 있다는 점에서 장점을 지닌다. 결과적으로는 65nm 공정에서 0.26mm<sup>2</sup>의 면적으로 211fs RMS jitter에 -68.1dBc fractional spur의 우수한 성능을 보여주었다.

## 저자정보

### 윤용노 박사과정 대학원생

- 소속 : 한국과학기술원 전기및전자공학부

- 연구분야 : Sensor Interface ICs, Frequency Generation ICs

- 이메일 : voogi3925@kaist.ac.kr

- 홈페이지 : <https://impact.kaist.ac.kr/>

# A-SSCC 2025 Review

단국대학교 파운드리공학과 석사과정 임재영

## Session 10 Low-Power Transceivers

이번 A-SSCC 2025의 Session 10에서는 저전력 무선 수신기 및 송수신기를 주제로 총 4 편의 논문이 발표되었다. 고선형성 RF 수신기, always-on wake-up receiver(WuRX), multi-band LPWAN 트랜시버, polar receiver 구조 등 다양한 저전력 무선 통신 아키텍처가 소개되었다. 본 리뷰에서는 #10.1과 #10.2 논문의 회로 구조와 동작 방식을 중심으로 정리한다.

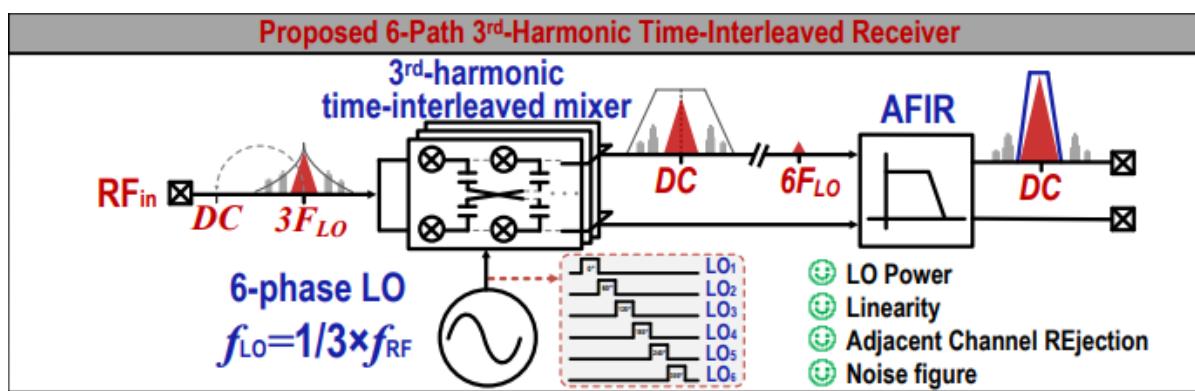

**#10-1** 본 논문은 중국 텐진대학교에서 발표한 논문으로, BLE 수신기에서 선형성과 전력 소모를 동시에 고려한 passive mixer 기반 RF front-end 구조를 제안하였다. 기존 zero-IF BLE 수신기에서는 RF와 동일한 주파수의 LO를 사용하는 passive mixer 구조로 인해, LO 고조파 성분과 switching nonlinearity로 인해 강한 blocker 환경에서 선형성 저하가 발생하는 문제가 있다. 이를 완화하기 위해 본 논문에서는 3<sup>rd</sup>-harmonic time-interleaved passive mixer 구조를 도입하였다. 제안된 수신기는 6-path non-overlapping LO를 이용한 6-path mixer를 기반으로 하며, LO 주파수를 RF 주파수의 1/3로 낮추어 LO buffer의 동작 주파수와 전력 소모를 감소시킨다. 또한 time-interleaving을 통해 mixer 스위칭에 따른 비선형 성분이 시간적으로 분산되도록 구성하였다. Mixer 이후에는 reconfigurable AFIR(Analog FIR) 필터를 적용하여 baseband 대역폭 설정과 인접 채널 신호 억제를 수행한다. AFIR 구조를 통해 baseband 필터링을 아날로그 영역에서 구현함으로써, 높은 선택도와 저전력을 동시에 달성한다. 측정 결과, 본 수신기는 OOB\_IIP3 26.5dBm, SFDR 80dB, 전력 소모 415uW를 달성하였다.

[그림 1] 제안된 6-path 3<sup>rd</sup>-Harmonic Time-Interleaved Receiver

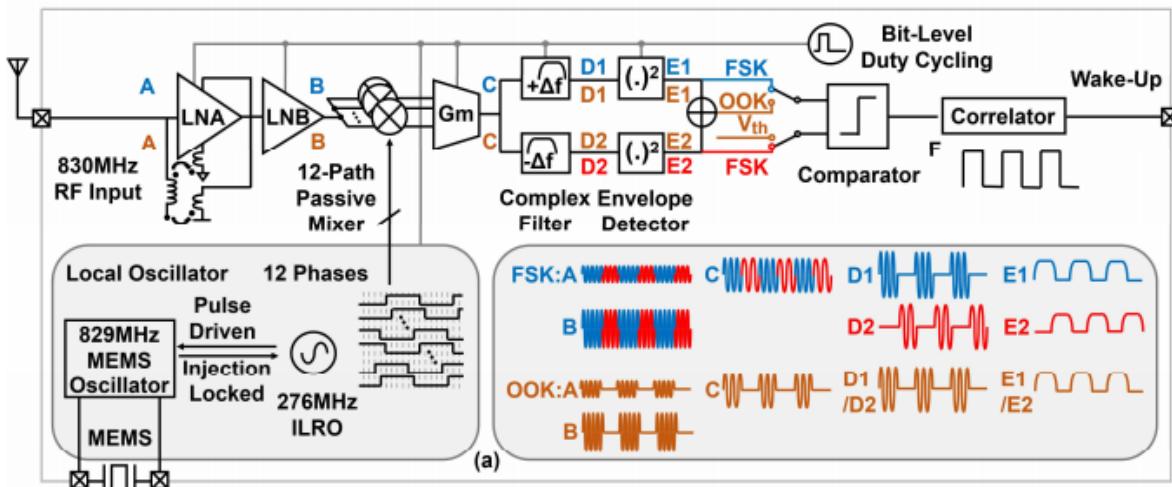

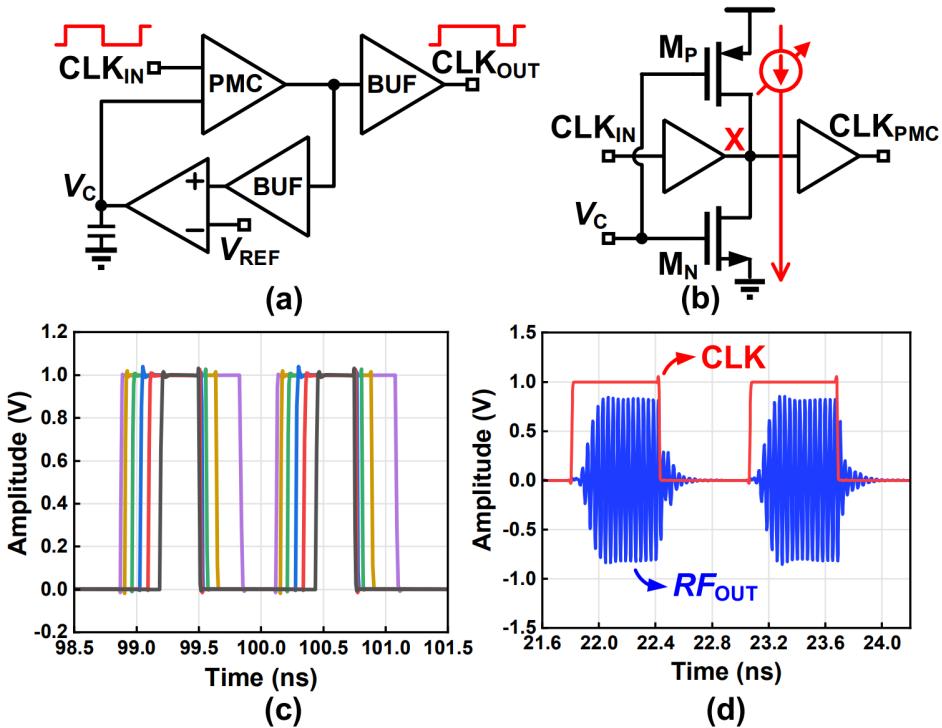

#10-2 본 논문은 싱가포르 난양공과대학교와 ASTAR에서 발표한 논문으로, OOK 및 FSK 신호를 대상으로 하는 초저전력 wake-up receiver(WuRX) 구조를 제안하였다. 기존 WuRX 구조에서는 RF front-end와 LO가 연속적으로 동작하는 경우가 많아, 항상 활성화된 상태에서의 전력 소모가 시스템 수명을 제한하는 요인으로 작용한다. 특히 연속 발진하는 LO와 RF front-end는 wake-up 신호가 존재하지 않는 대부분의 시간 동안에도 전력을 소모하게 된다. 이를 줄이기 위해 본 논문에서는 sub-sampling 기반 RF front-end와 duty-cycled 동작 방식을 채택하였다. RF 입력 신호는 12-path passive mixer를 통해 시간 영역에서 sub-sampling되며, 이후 저주파 성분으로 변환된다. 이 과정에서 RF front-end는 연속 동작하지 않고, 신호 검출에 필요한 구간에서만 활성화된다. Mixer 이후에는 complex envelope detector가 배치되어 RF 신호의 진폭 정보를 추출한다. OOK 신호의 경우 진폭 변화가 직접적으로 envelope에 반영되며, FSK 신호의 경우 주파수 차이에 따른 envelope 패턴의 차이가 후단에서 구분된다. 추출된 envelope 신호는 comparator를 통해 디지털 신호로 변환되며, correlator에서 미리 정의된 패턴과 비교되어 wake-up 여부가 결정된다. LO 생성부에는 pulse-driven MEMS oscillator가 사용되었다. MEMS 공진기는 injection-locked 방식으로 구동되며, 연속 발진 대신 펄스 형태의 구동 신호를 이용하여 평균 구동 에너지를 줄인다. 또한 12-phase ILRO 구조를 통해 sub-sampling mixer 구동에 필요한 non-overlapping clock이 생성된다. 제안된 WuRX는 RF front-end, LO, baseband 블록이 모두 bit-level duty cycling 방식으로 동작하도록 구성되어 있다. 측정 결과, 본 수신기는 930nW 전력 소모에서 OOK -93dBm, FSK -90dBm의 sensitivity를 달성하였다.

[그림 2] 제안된 pulse-driven MEMS oscillator 기반 WuRX 구조

## 저자정보

### 임재영 석사과정 대학원생

- 소속 : 단국대학교

- 연구분야 : clock generators

- 이메일 : lgy72250338@dankook.ac.kr

- 홈페이지 : <https://sites.google.com/dankook.ac.kr/acs-lab>

# A-SSCC 2025 Review

고려대학교 전기전자공학부 석사과정 심승우

이번 2025 IEEE ASSCC Symposium에서는 Wireless 관련 다섯 개의 세션이 열렸다. 이 중 본 리뷰에서는 Session 13에서 K,Ka-band 대역의 phase array system 두 편, 그리고 Session 17에서 Ka-band oscillator 논문까지 총 세 편을 다룬다

## Session 13 Phased-Array System and Components

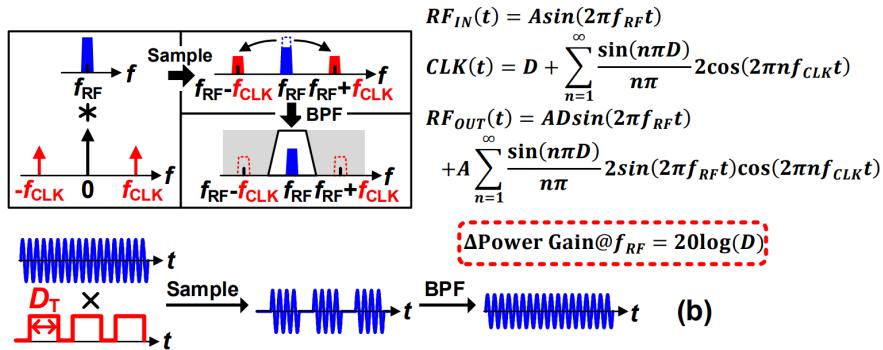

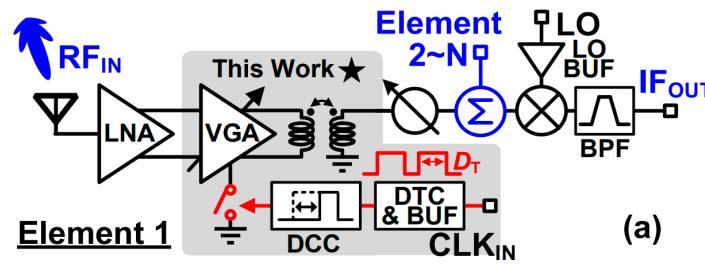

**#13-1** 이번에 리뷰할 논문은 도쿄공업대학의 Kenichi Okada 교수님 그룹에서 발표한 "A Ka-Band Time-Modulated Variable Gain Amplifier with 30-dB Gain Tuning and <0.1-Degree Phase Variation via Duty Cycle Control"이다. 6G 및 위성 통신을 위한 Phased array system에서 gain control과 beamforming을 위해 variable gain amplifier(VGA)가 필수적이다. 하지만 current-steering이나 gilbert-cell 같은 기존의 기법들은 gain tuning range가 제한적이고, gain이 변할 때 phase variation이 심한 단점이 있습니다. 본 논문은 이러한 문제를 해결하기 위해 Time-Modulated Scheme를 적용했습니다. 핵심 아이디어는 별도의 clock signal의 duty cycle을 조정하여 VGA의 gain을 바꾼다는 아이디어이다. 그림 1에서 볼수있듯 rf신호가 clock 신호에 의해 sampling이 되는 과정에서 원치 않는 harmonic 성분들이 발생 하지만, 추가적인 band pass filter를 통해 원하는 RF 신호만 출력한다는 것이다. 이 방식의 이론적 차이는 Duty Cycle(D)에 따라  $20\log D$ 로 결정된다. 또한 duty cycle의 정밀한 조정을 위해 그림 2에 나오는 dcc(duty cycle control) loop과 PMC(pulse modification cell)을 설계 및 구현하였다. CMOS 65nm 공정으로 설계되었고, 코어 면적은 1150 um x 280 um이며, gain에 따라 4.9 mW에서 103 mW의 파워를 소모한다. 측정결과 maximum gain은 29.6dB, 24 GHz에서 29.7 GHz의 3dB bandwidth와 DCC를 통해 30 dB의 gain control range를 가지고 또한 gain이 변할 때 phase는 0.1도 미만으로 변했으며 OP1dB는 28GHz에서 12.5dBm이 측정되었다. time modulated 구조를 통해 ka-band에서 30dB의 넓은 gain control range내에서도 phase variation이 0.1도 미만으로 유지되어, 우수한 phase stable한 기법을 제안하였다.

그림 1.(a) Architecture of the time-modulated RX; (b) Illustration of time-modulated VGA operation in frequency and time domains

그림 2. Schematics of (a) DCC loop and (b) pulse modification cell; Simulated results of (c) duty cycle tuning by VREF and (d) transient

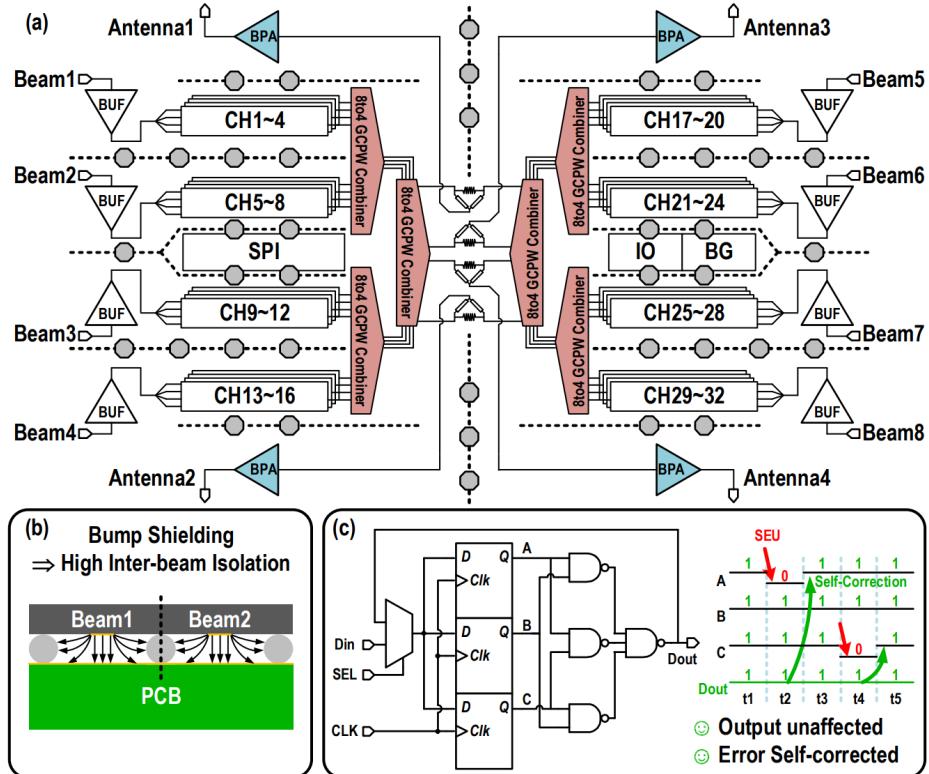

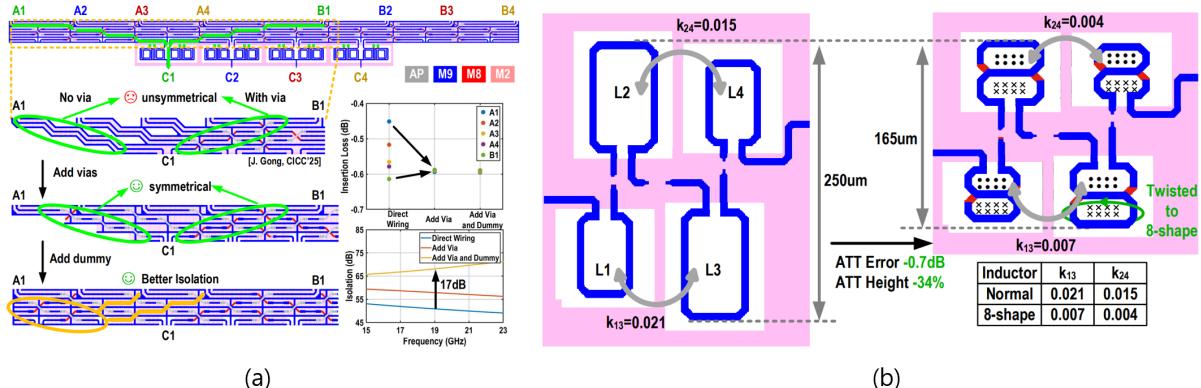

#13-2 이번에 리뷰할 논문은 칭화대학교의 Baoyong Chi 교수님 그룹에서 발표한 "A K-Band 8-Beam 4-element Phased-Array Transmitter Using GCPW-based Beam-combining Network and Compact 8-shaped Coils for Satellite Communications"이다. 저궤도(LEO) 위성통신과, 5G 비지상망(NTN)의 down-link로 사용되는 K-band에서는 높은 path loss로 인해 multi-beam phased array system이 필요하다. 하지만 on-chip multi beam 시스템을 구현시에 다수의 functional block 집적에 따른 레이아웃의 복잡성, Block 간 isolation의 어려움, 우주 극한 환경에서의 신뢰성 문제가 있다. 본 논문은 이것을 해결하기위해 GCPW(grounded coplanar waveguide) wiring 구조와, 개선된 8-shaped coil technique를 제안하였다. 그림3에 전체 블록도처럼 8개의 beam이 들어오고, 각 4개의 channel을 거쳐 32개의 output이 합쳐져 4개의 balanced power amplifier를 통해 신호가 출력되는데, 이때에 Flip chip packaging에 사용되는 bump를 path사이에 배치하여 isolation을 향상시켰고 우주 환경의 방사선에 의한 SEU(single event upset) 오류를 방지하고자 Majority Voting Logic 기반의 Fault-tolerant Register cell을 설계하여 SPI(serial peripheral interface)의 신뢰성을 높였다. 그림 GCPW combining network에 jumper들이 line의 bend마다 대칭적으로 배치하여 gain matching을 향상시키고 dummy trace들로 signal간의 coupling을 막아 0.15 dB의 gain mismatch 감소와 17dB의 Inter-beam isolation을 향상시켰으며, 그림 3에 나와있는 개선된 8-shape coil구조를 통해 34%의 면적감소와 0.7dB의 Attenuation 정확도 향상을 보였다. CMOS 65nm 공정으로 설계되었고 전체 칩은 7.32mm x 4.52mm이며 채널당 45.3mW를 소모하였다. 측정결과 17.2 GHz에서 21 GHz의 3dB bandwidth와 32개 채널간의 0.8dB의 Gain mismatch를 보였다. 제안된 구조를 통해 동시에 8개의 beam을 지원하는 phased array transmitter를 구현하였고 multi beam beamformer 디자인에 효율적인 기법을 제안하였다.

그림 3.(a) Block diagram of the proposed phased-array TX (b) bump shielding between beams (c) SEU-resilient register cell.

그림 4.(a) The proposed GCPW-based 8-to-4 beam-combining network and comparison of different GCPW wiring schemes, (b) The proposed 8-shape coil technique.

## Session 17 Oscillators

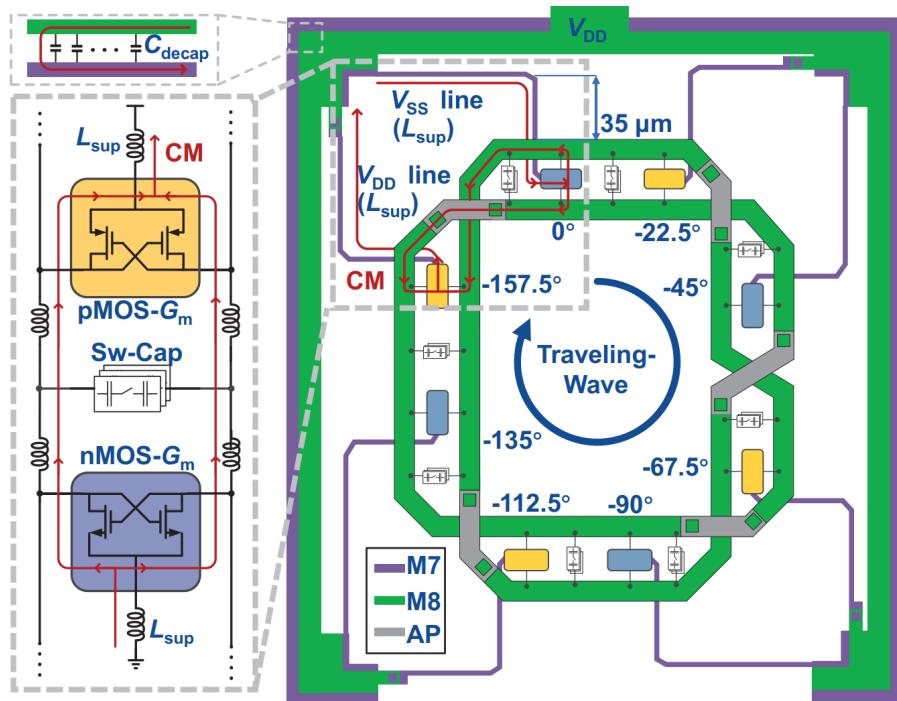

**#17-2** 이번에 리뷰할 논문은 중국 과학기술대학교(USTC)의 Yizhe Hu 교수님 그룹에서 발표한 "A 25.48-29.25 GHz Rotary Traveling-Wave Oscillator Achieving -191 dBc/Hz FoM at 10MHz Offset Using Ring-Interleaved N/P Cross-Coupled Pairs in 22-nm CMOS"이다. 6G 통신이나 AI 프로세서같은 시스템에서 High-speed multi-phase clock generation이 필수적이다. RTWO(rotary traveling wave oscillator)는 multi-phase 신호를 생성하는데 구조적으로 장점이 있지만, Switched capacitor(sw-cap)와 -Gm cell이 결합되어 있었는데 그로인해 기존 LC oscillator에 비해 Phase noise 성능이 안좋다는 단점이 있습니다. 본 논문은 Ring-Interleaved Nmos/Pmos Cross-Coupled Pairs 구조를 제안했습니다. 기존의 Back to back 인버터 구조가 8개의 코어를 이용하여 8개의 differential 신호 즉 16개의 phase를 생성한 반면, 본 논문은 4개의 Nmos pair와 4개의 Pmos pair를 Interleave하여 배치하였고, 그로인해 코어들간의 matching inductor인 Mobius Ring을 Common mode inductor로 사용하여 추가면적 없이 높은 Common mode impedance를 형성하여 Flicker noise upconversion을 억제하였고, sw-cap을 Nmos와 Pmos pair의 중앙에 배치하여 3차 하모닉성분이 Capacitive path 대신 Inductive path로 흘러들어가 추가적으로 Flicker noise upconversion을 막아 phase noise를 향상시켰다. CMOS 22nm 공정을 이용하여 설계되었고 25.48GHz에서 29.25GHz로 tuning range가 13.7%이고 1MHz에서 -105.1dBc/Hz의 phase noise가 측정되었고, 전력소모도 8.8mW로 매우 낮아 RWTO 구조중에 처음으로 FoM(figure of merit)가 -190 dBc/Hz를 넘겼다. 본 논문은 Nmos,Pmos pair를 통해 LC oscillator 급의 성능을 가진 RWTO 기법을 제안하였다.

그림 5.(a) The proposed RTWO with ring-interleaved N/P cross-coupled MOS pairs and a dedicated supply scheme.

## 저자정보

심승우 석사과정 대학원생

- 소속 : 고려대학교 전기전자공학과

- 연구분야 : mm-Wave IC design

- 이메일 : lisang@korea.ac.kr

- 홈페이지 : <https://arfsi.korea.ac.kr>

# A-SSCC 2025 Review

KAIST 전기및전자공학부 석박사통합과정 이동윤

## Session 28 Advanced Transceivers

최근 무선 통신 시스템은 더 높은 데이터 전송률과 극한 환경에서의 안정성을 동시에 요구한다. Session 28에서는 이러한 요구에 부응해, 기존 수신기 아키텍처의 한계를 새로운 루프 제어 기술로 돌파한 Polar PT-RX와, 밀리미터파 대역에서 온도 변화에 따른 성능 저하를 원천 차단한 Temperature-Compensated LNA 기술이 발표되었다.

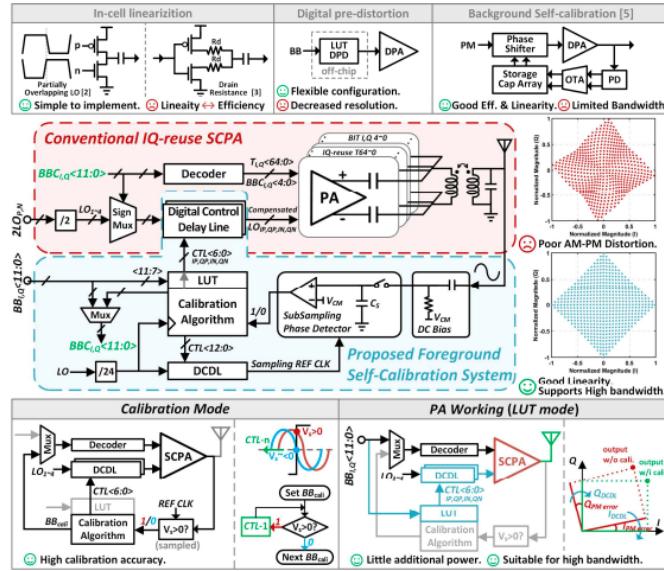

### #28-2 Coherent Polar PT-RX

28.2 "A Coherent Polar PT-RX for 32-APSK/16-QAM/GFSK Demodulation with High ACR and Relaxed I/Q Generation"은 기존의 Phase-Tracking Receiver (PT-RX)가 가진 구조적 한계를 극복하고, 고차 변조 방식(High-order Modulation)과 강력한 간섭 제거(ACR) 성능을 동시에 달성한 새로운 수신기 아키텍처를 제안한다.

기존 PT-RX는 저전력 특성이 뛰어나지만, 위상 동기 루프(PLL) 기반 동작 특성상 Loop Bandwidth와 Stability(안정성) 간의 트레이드오프가 심했다. 대역폭을 좁히면 간섭 신호는 잘 거르지만 루프가 불안정해지고, 대역폭을 넓히면 루프는 안정되나 인접 채널 간섭 (ACR)에 취약해지는 딜레마가 있었다. 또한, 위상 정보만 추적하기 때문에 진폭 정보가 포함된 QAM 같은 고차 변조 신호를 복조하기 어렵다는 치명적인 단점이 있었다.

이 논문은 두 가지 핵심 기술로 이 문제를 해결했다.

Additional Zero for Stability: 루프 내에 Delay-Locked Loop (DLL) 기반의 추가적인 Zero를 삽입하는 기법을 도입했다. 이를 통해 루프 대역폭을 좁혀 간섭 제거 성능을 극대화하면서도, 충분한 위상 마진을 확보해 시스템이 발진하지 않도록 안정성을 잡았다. 그 결과 Closed-loop RX 중 최고 수준의 ACR 성능을 달성했다.

Coherent Polar Demodulation: 진폭(Amplitude)과 위상(Phase)을 분리해 처리하되, 이를 다시 결합하여 복조하는 Coherent Polar 구조를 채택했다. 덕분에 기존 PT-RX에서는 불가능했던 32-APSK나 16-QAM 같은 진폭 변조가 포함된 신호도 정확히 복조할 수 있게 되었으며, I/Q 경로 간의 부정합(Mismatch) 문제에서도 자유로워졌다.

결과적으로 이 수신기는 2.4GHz 대역에서 동작하며, 기존 PT-RX의 저전력 장점을 유지하면서도 고성능 통신 규격을 만족시키는 차세대 수신기 솔루션으로 평가받는다.

[그림 1] 본 연구에서 제시하는 DPA 구조와 선행연구의 비교

## #28-5 Temperature-Compensated mmWave LNA (PILTOM)

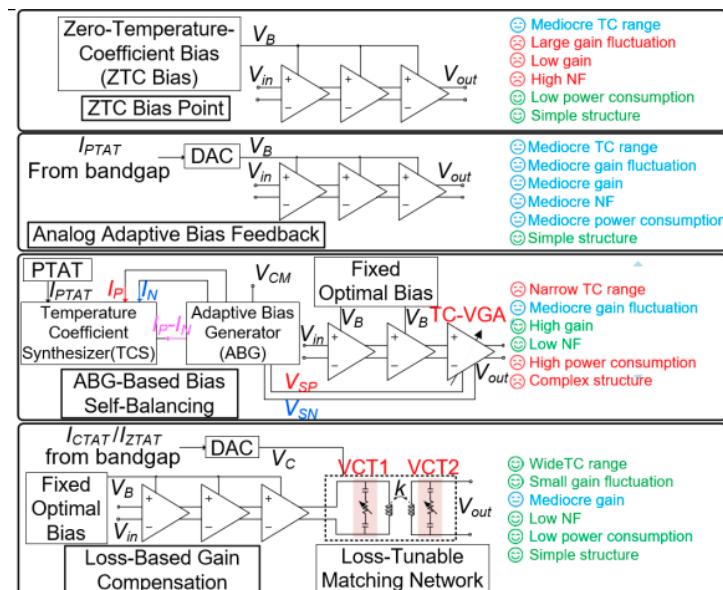

28.3 "A 26.2-41.3 GHz Temperature-Compensated LNA with Phase-Invariant Loss-Tunable Output Matching Achieving  $\pm 0.0011$  dB/ $^{\circ}$ C Gain Variation Across  $-55$   $^{\circ}$ C to  $125$   $^{\circ}$ C"은 5G NR(28/39GHz) 및 위성 통신(Ka-band)을 위한 밀리미터파 LNA가 극한의 온도 환경( $-55^{\circ}$ C ~  $125^{\circ}$ C)에서도 일정한 성능을 유지하도록 하는 혁신적인 보상 기술을 제안한다.

밀리미터파 시스템은 옥외 기지국이나 위성 탑재체처럼 온도 변화가 극심한 환경에 노출된다. 기존에는 온도가 변하면 트랜지스터의 바이어스 전압을 조절해 이득(Gain)을 맞추려 했으나, 이 경우 잡음지수(NF)나 선형성(Linearity)의 최적 동작점이 틀어지는 문제가 발생했다. 혹은 별도의 가변 이득 증폭기(VGA)를 추가해 이득을 보정하기도 했지만, 이는 전력 소모와 칩 면적을 증가시키고 위상(Phase)이 틀어지는 부작용을 냈다.

핵심 원리는 다음과 같다. 트랜지스터의 바이어스는 온도가 변해도 항상 최적의 성능(최저 잡음, 최고 선형성)을 내는 지점에 고정한다. 대신, LNA의 출력 매칭 네트워크에 손실(Loss)을 미세하게 조절할 수 있는 기능을 넣어서, 온도가 낮아져 이득이 커지면 손실을 늘리고, 온도가 높아져 이득이 줄면 손실을 줄이는 방식으로 전체 이득을 일정하게 유지한다.

그리고 단순히 손실만 조절하면 위상이 변할 수 있는데, 이 회로는 가변 저항 역할을 하는 VCT와 Transformer를 정교하게 결합해, 손실을 조절해도 위상은 변하지 않도록 설계했다.

이 기술이 적용된 65nm CMOS LNA는 26.2~41.3 GHz라는 매우 넓은 대역에서 동작하며, -55°C에서 125°C까지 온도가 변하는 동안 이득 변화율이  $\pm 0.0011$  dB/°C에 불과할 정도로 완벽에 가까운 온도 보상 성능을 보여주었다. 이는 추가적인 전력 소모나 면적 증가 없이도 시스템 신뢰성을 획기적으로 높일 수 있는 기술로, 향후 6G 및 우주 통신 분야에서의 활용도가 매우 높을 것으로 기대된다.

[그림 2] 본 연구에서 제시하는 H-PCA 구조와 선행연구의 비교

## 저자정보

### 이동윤 석박사통합과정 대학원생

- 소속 : KAIST

- 연구분야 : Body-Channel-Communication Transceiver

Design for Body-Area Network in Biomedical Application

- 이메일 : [dongyoong.lee@kaist.ac.kr](mailto:dongyoong.lee@kaist.ac.kr)

- 홈페이지 : <https://impact.kaist.ac.kr>